Basiseigenschappen transistors#

In deze cursus bespreken we de werking en het ontwerp van analoge circuits. Hiervoor is een goed inzicht van de transistors die hierbij gebruikt worden noodzakelijk. Daarom bespreken we in dit hoofdstuk de karaakteritieken van de MOS en de bipolaire transitors.

MOSFET transistors#

We gebruiken in de elektronica 2 types Metaal Oxide Semiconductor Field Effect Transistors (MOSFET). We bespreken in dit hoofdstuk de planaire MOS transistors. Sinds 2015 zijn er voor de meest geavanceerde digitale technologien ook andere hardware implementaties in gebruik. Aangezien deze hardware implementaties momenteel enkel voor digitale hardware gebruikt wordt, gaan we op de niet-planaire MOSFET technologien niet verder in in dit hoofdstuk. De klassieke planaire MOS transistor bestaat uit een gate gemaakt uit polykristallijn Silicium (afgekorte poly) die neergelegd wordt boven op een heel dun oxide dat op het Silicium neergelegd is. Daarnaast zijn er source en een drain gebieden geïmplanteerd die aan de hand van een pn-junctie gescheiden zijn van de bulk.

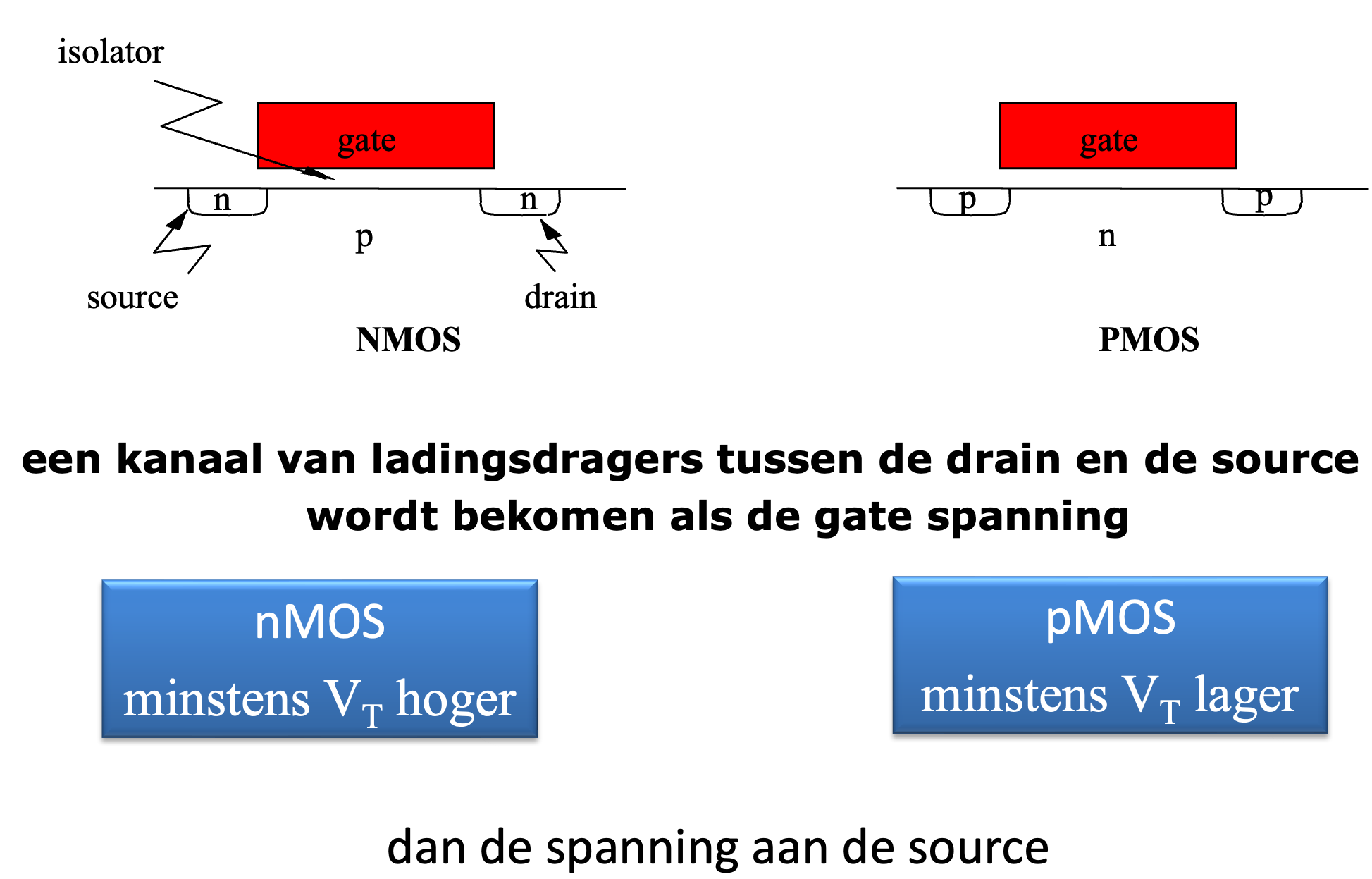

De n-kanaal MOSFET (nMOS) wordt geïmplementeerd in een laag gedopeerde p-well. Daarom komt achtereenvolgens een dun gate oxide (als isolator) en een poly-kristalijne gate. In een volgende stap worden dan vervolgens de hooggedopeerde source en drain structuren gedefinieerd door n-type implantatie, waarbij de gate het kanaal afschermt.

De p-kanaal MOSFET (pMOS) wordt geïmplementeerd in een laag gedopeerde n-well. Daarom komt achtereenvolgens een dun gate oxide (als isolator) en een poly-kristalijne gate. In een volgende stap worden dan vervolgens de hooggedopeerde source en drain structuren gedefinieerd door p-type implantatie, waarbij de gate het kanaal afschermt.

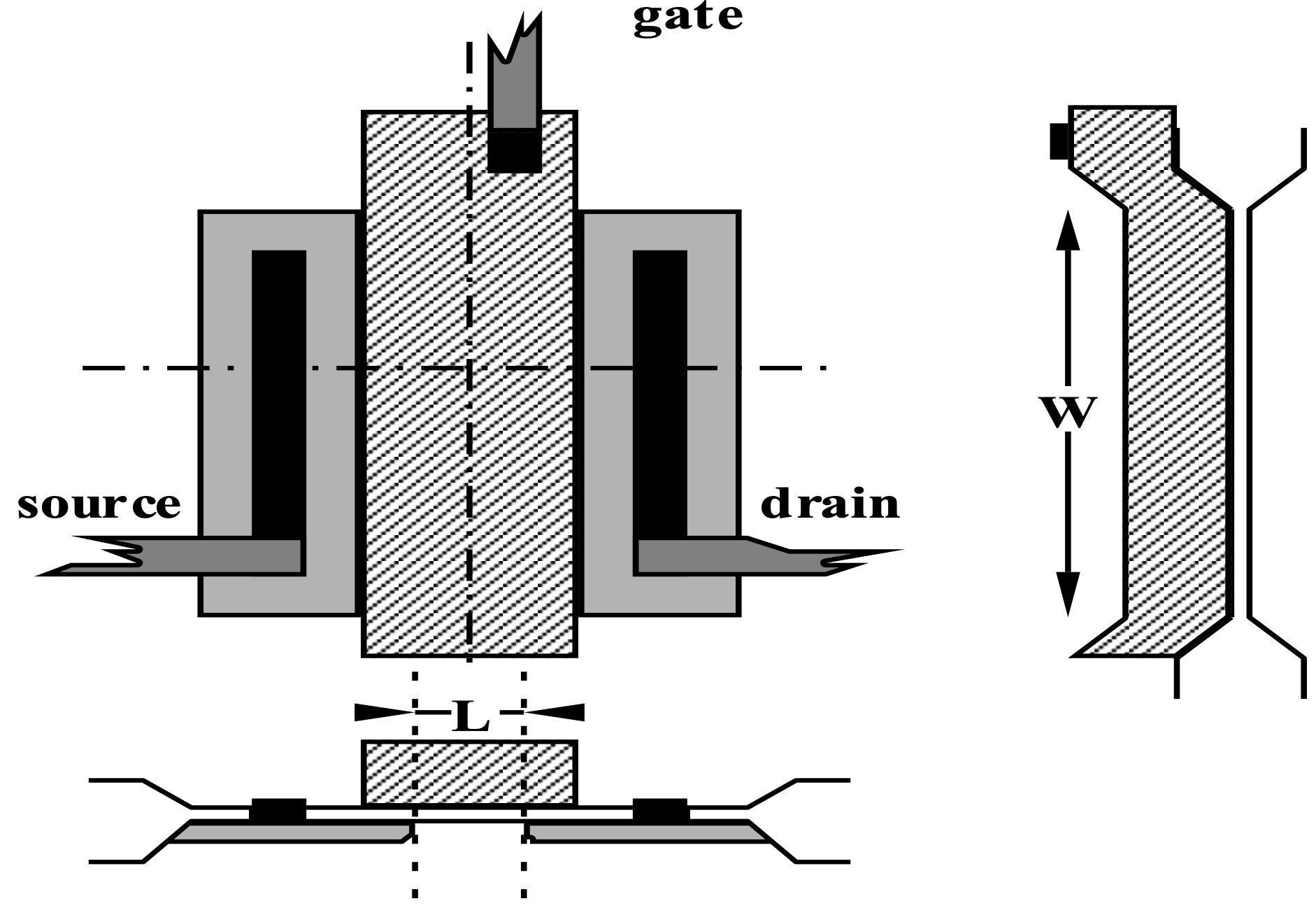

Figuur 1 toont een schematische doorsnede van de planaire MOS transistor langs een snede van source naar draain.

Figuur 1 Schematische doorsnede van de planaire MOS transistor#

Wanneer we een spanning aanleggen aan de gate, moeten we eerst zorgen dat ladingsdragers van de bulk, die van een tegengesteld type zijn dan de gewenste ladingsdragers, voldoende ver van onder de gate verdwijnen. Vervolgens trekken we met de gate ladingsdragers uit de source aan die een kanaal gaan vormen onder de gate. Hoe hoger de spanning aan de gate, hoe meer ladingsdragers in het kanaal.

Voor een nMOS transistor hebben we een positieve spanning nodig aan de gate, omdat het kanaal uit elektronen bestaat (=negatieve ladingsdragers). Bovendien moet die spanning groter zijn dan de spanning aan de source plus de drempelspanning \(V_T\).

Voor een pMOS transistor hebben we een negatieve spanning nodig aan de gate, omdat het kanaal uit gaten bestaat (=positieve ladingsdragers). Bovendien moet die spanning kleiner zijn dan de spanning aan de source min de drempelspanning \(V_T\).

Eerst bekijken we een dwarsdoorsnede van een nMOS met <\(V_{GS}\)<\(V_T\) en \(V_{DS}\)=VSB= 0V. Zolang de gate-source spanning kleiner blijft dan de drempelspanning zal de toenemende gate spanning in de eerste plaats gecompenseerd worden door een vergroting van de ruimteladingslaag onder de gate. De gaten verdwijnen onder de gate en dit de negatieve lading die de toenemende positieve lading op de gate compenseert. Van zodra dat de gate-source spanning groter wordt dan de drempelspanning bekomen we een kanaal onder de gate, zoals zichtbaar is in de dwarsdoorsnede van een nMOS met \(V_{GS}\)>\(V_T\)> en \(V_{DS}\)=VSB= 0V. Hoe meer we de gate spanning verder laten toenemen, hoe meer lading we in het kanaal bekomen. [] http://www-g.eng.cam.ac.uk/mmg/teaching/linearcircuits/mosfet.html

Figuur 2 Bovenaanzicht MOS transistor, tesamen met 2 doorsnedes (onder) doorsnede langs de source-drain as (rechts) doorsnede loodrecht op het kanaal#

In de praktijk kunnen we de gate niet perfect naast de source leggen, omdat perfectie niet bestaat. We kunnen die perfectie wel altijd beter en beter proberen te benaderen. Dit maakt deel uit van de constante technologische evolutie. We kunnen ons niet permitteren dat er een onderbreking in het kanaal is. Dus zal er in de praktijk steeds een overlap zijn tussen de gate en de source en ook tussen de gate en de drain. Van de andere kant mag de dopering ook niet zo ver onder de gate diffunderen dat er een kortsluiting zou kunnen ontstaan tussen drain en source.

In het symbool van de MOS transistor wordt zeer goed aangegeven dat de gate een condensator is die moet opgeladen worden. Voor de rest zijn er een aantal alternatieven in gebruik. De symbolen aan de linkerkant, zowel voor de nMOS als voor de pMOS geven goed aan dat de source, de drain en ook het kanaal, als het er is, een PN junctie vormen met de bulk. De richting van de pijl geven weer de richting van de pn-diode aan. Dit symbool is nuttig wanneer we aan de transistor een bulkspanning opleggen die niet de normale waarde is (voeding voor de pMOS of grond voor de nMOS). Het komt ook wel voor, als variatie op dit symbool, dat de pijl aan de kant van de source is getekend. In dit geval is de richting van de pijl omgekeerd. De symbolen aan de rechterkant zijn veel eenvoudiger en laten dus toe veel sneller een schema te tekenen. Hierbij veronderstellen we dat het bulkcontact steeds de grond is voor de nMOS en de voeding voor de pMOS. Het bolletje aan de gate van de pMOS wordt in de elektronica vaak gebruikt om een inversie van een signaal aan te duiden, en het geeft hier aan dat de transistor in geleiding is als de spanning aan de gate laag is.

Korte Herhaling Bipolaire transistors#

Ook de emitter en de collectorweerstand van de bipolaire transistor zijn belangrijk, vooral omdat de stromen die hierdoor lopen veel groter zijn dan de stromen door de basis. De emitterweerstand kan kleiner gemaakt worden door deze laag dunner te maken en de collectorweerstand door de laag dikker te maken. Soms wordt er om een kleinere collectorweerstand te bekomen nog een zeer hoog gedopeerde laag voorzien helemaal onderaan de structuur. De weerstandswaarden die hierboven opgegeven zijn gelden voor een npn transistor. Omwille van de slechtere geleidbaarheid van een p-type laag zullen we hogere r_{e} en r_{c} waardes bekomen voor een pnp transistor.

N-type laag heeft bij gelijke dopering een beduidend lagere weerstand dan een P-type laag

Een pnp transistor heeft dus veel grotere emitter en collector weerstanden in vergelijking met een npn transistor

Voor vermogencomponenten kunnen deze weerstanden en de opwarming die erbij hoort een probleem vormen