Klasse B versterkers#

Inleiding#

In Tabel 2 hernemen we een overzicht van de verschillende versterkers die we bespreken in de leerlijn analoge elektronica. In het vorige hoofdstuk bespraken we de laagfrequent versterkers die slechts 1 vermogentransistor gebruiken in de laatste trap (daar waar het meeste vermogen verbruikt wordt). In dit hoofdstuk bespreken we de laagfrequent versterkers die 2 of meer vermogentransistor gebruiken in de laatste trap. Dit geeft een duurder ontwerp van de versterker, maar zoals we later zullen zien, geeft dit een veel efficiëntere implementaties. Als een gevolg hiervan kan de duurdere aanschafkosten gemakkelijk teruggewonnen worden door het lager energieverbruik.

laagfrequent of breedband |

hoogfrequent of resonant |

|

|---|---|---|

1 transistor in de vermogentrap |

Klasse A |

Klasse C |

2 of meer transistors in de vermogentrap |

Klasse B |

Klasse D |

Basisschema#

Schema voor DC werking#

Figuur 29 toont het basisschema van de Klasse B versterker. We herkennen een bipolaire npn en pnp transistor. Beide transistors staan in gemeenschappelijke collector configuratie. Op deze manier werkt de vermogentransistor als stroomversterker. De spanning aan de basis wordt (op de redelijk constante basis-emitter offset na) doorgegeven naar de collector. De stroom aan de collector wordt echter met de factor \(\beta_F\) van de bipolaire transistor versterkt.

Figuur 29 Basisschema van de klasse B versterker voor DC werking.#

Het is belangrijk in dit schema de verschillende bouwblokken te herkennen. Figuur 30 toont deze bouwblokken. We hebben natuurlijk in de eerste plaats de belasting \(R_L\). Deze wordt hier symbolish weergegeven als een weerstand, maar kan in de praktijk eender welke actuator zijn die vermogen opneemt in fase met de belasting.

Daarnaast zien we (in de groene box) zowel het pull-up netwerk als het pull-down netwerk aangeduid.

In het schema van Figuur 29 zien we dat er zowel een AC-pad als een DC-pad tussen beide voedingen (\(V_{DD}\) en -\(V_{DD}\)) en de belasting mogelijk is.

Figuur 30 Basisschema van de klasse B versterker voor DC werking met aangeduide bouwblokken.#

Om dit schema te kunnen simuleren in SPICE, geven we nummers aan de verschillende knopen, zoals je kan zien in Figuur 31. Deze nummers kan je dan vervolgens terugvinden in de spice-listing.

Figuur 31 Basisschema van de klasse B versterker voor DC werking.#

Klasse B versterker

*

* SUPPLY VOLTAGES

VPOS 8 0 DC +15V

VNEG 9 0 DC -15V

*

* input source

VS1 1 0 DC 0 SIN(0V 5VPEAK 10KHZ)

*

* PUSH-PULL TRANSISTOR OUTPUT STAGE

Q1 8 1 2 QNPN

Q2 9 1 2 QPNP

*

* Load resistance

RL1 2 0 100

*

* DEVICE MODELS

.model QNPN NPN(BF=50)

.model QPNP PNP(BF=50)

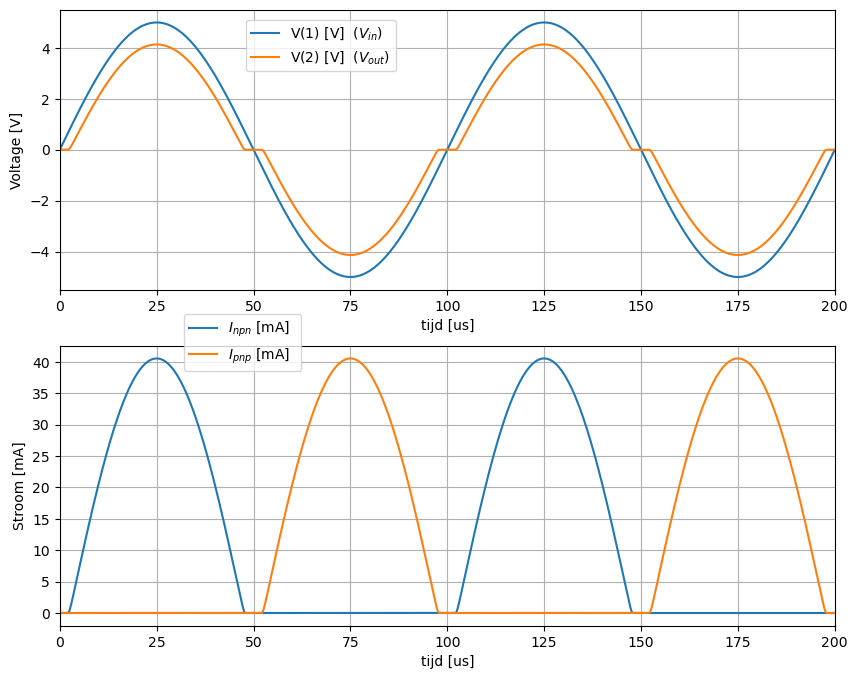

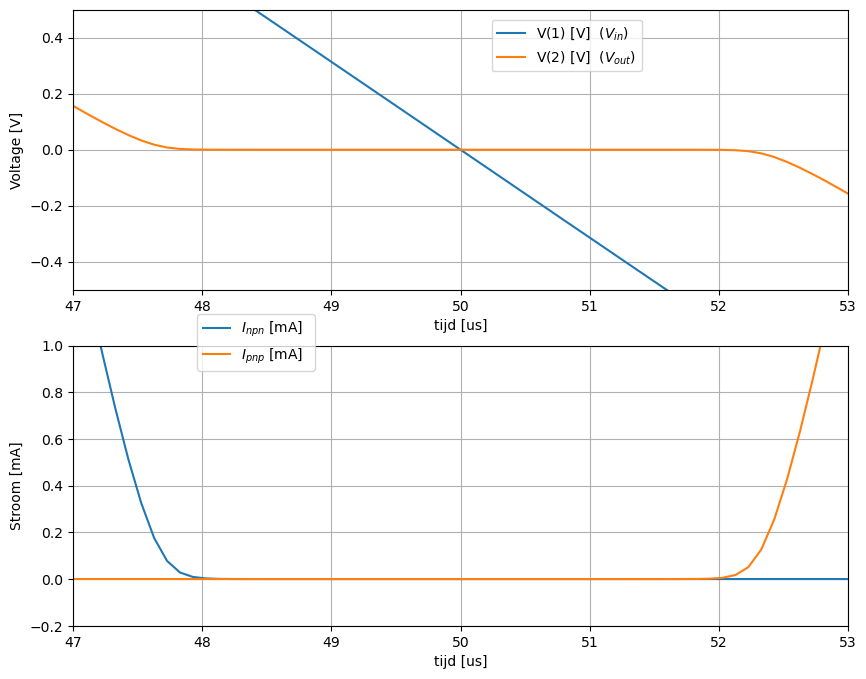

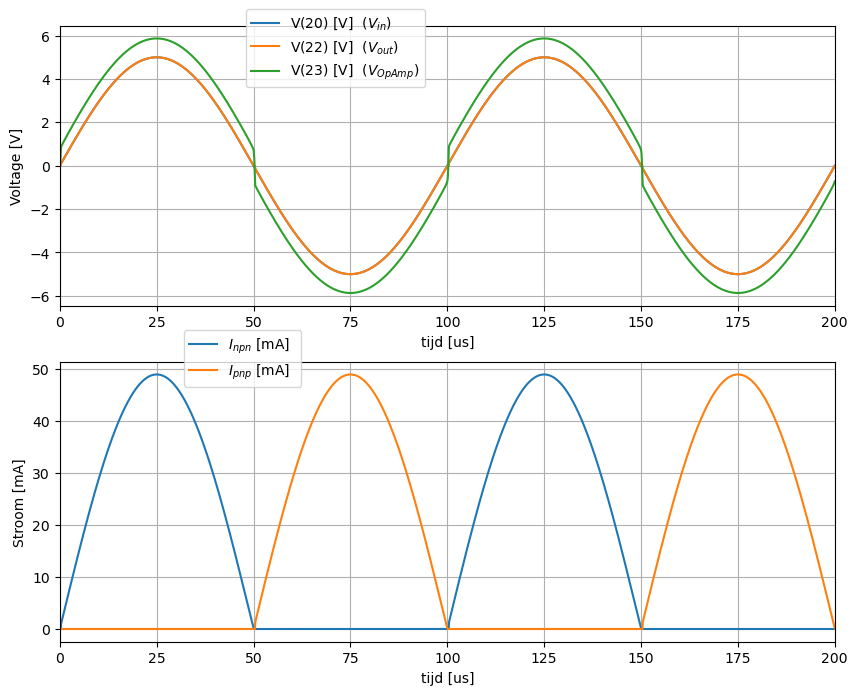

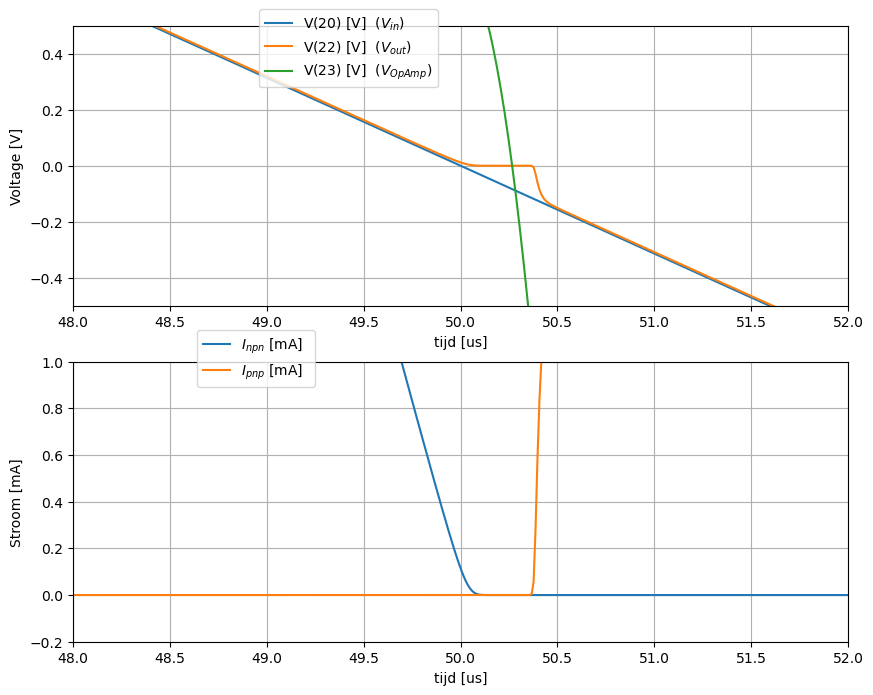

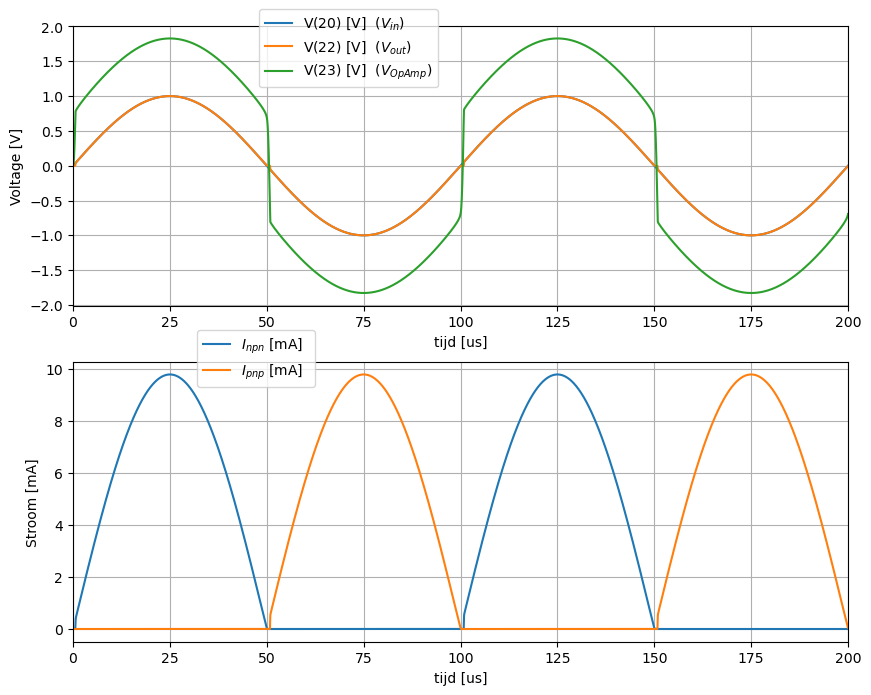

De simulatie (zie Figuur 32) van de spice code listing1 geeft duidelijk de dode zone aan bij de nuldoorgang van de spanning. In Figuur 33 bekijken we deze nuldoorgang in meer detail.

Figuur 32 De klasse B versterker: de stromen en spanningen als functie van de tijd.#

Figuur 33 De klasse B versterker: detail van de stromen en spanningen als functie van de tijd in de buurt van de nuldoorgang.#

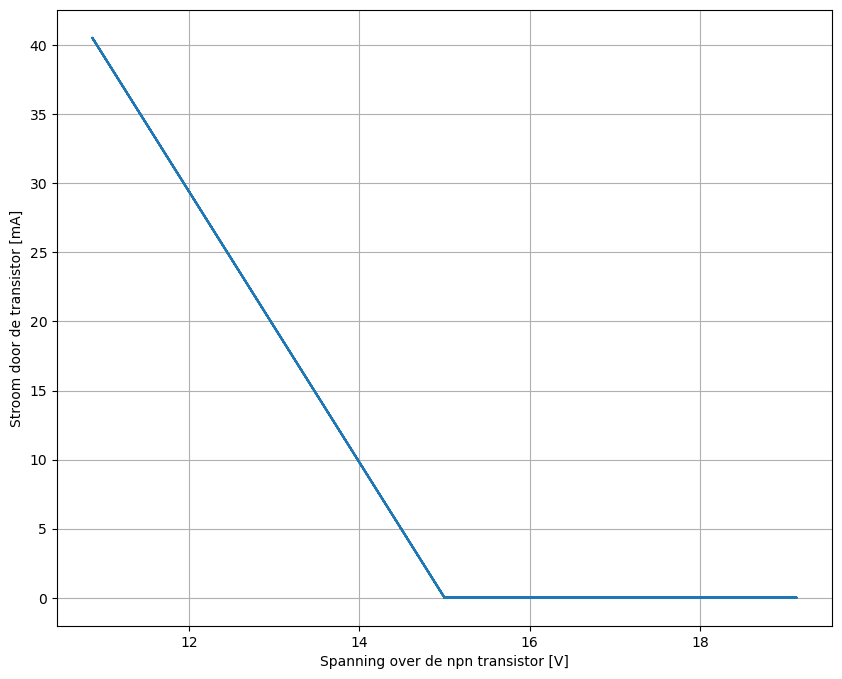

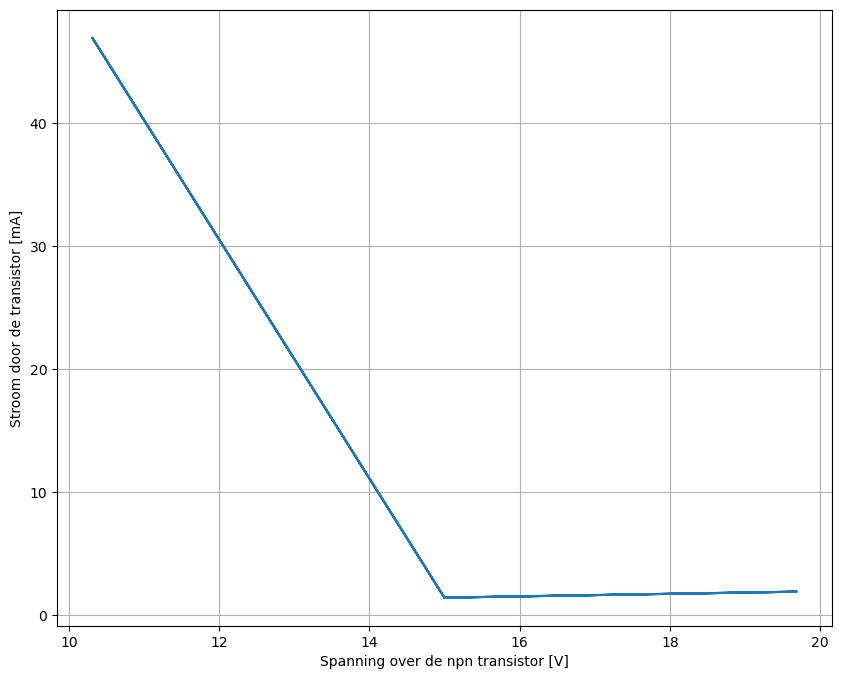

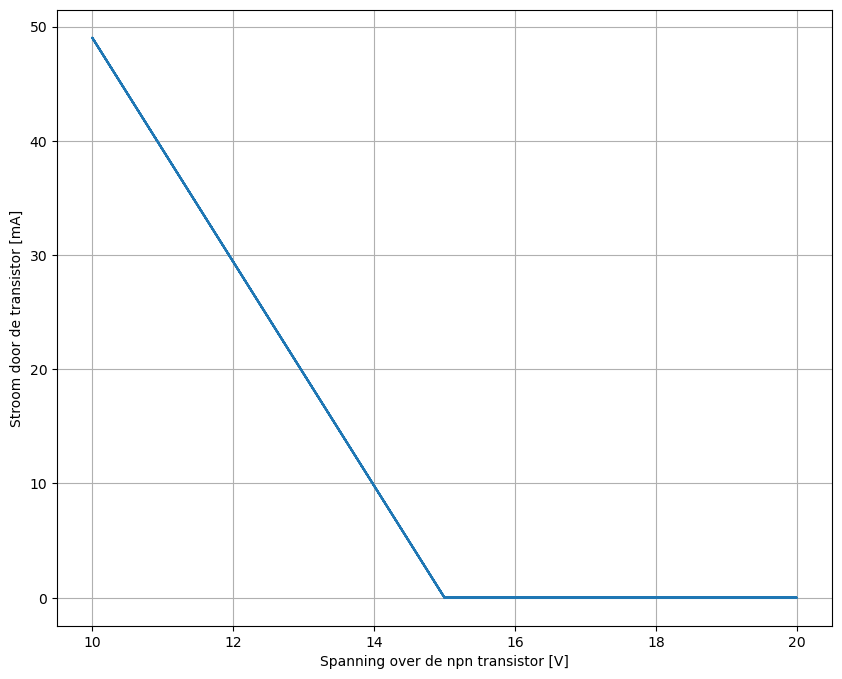

Figuur 34 toont de stroom door als functie van de spanning over de transistor voor de npn transistor. Voor de pnp transistor bekomen we dezelfde grafiek.

Figuur 34 De klasse B versterker: de stroom door een npn transistor als functie van de spanning.#

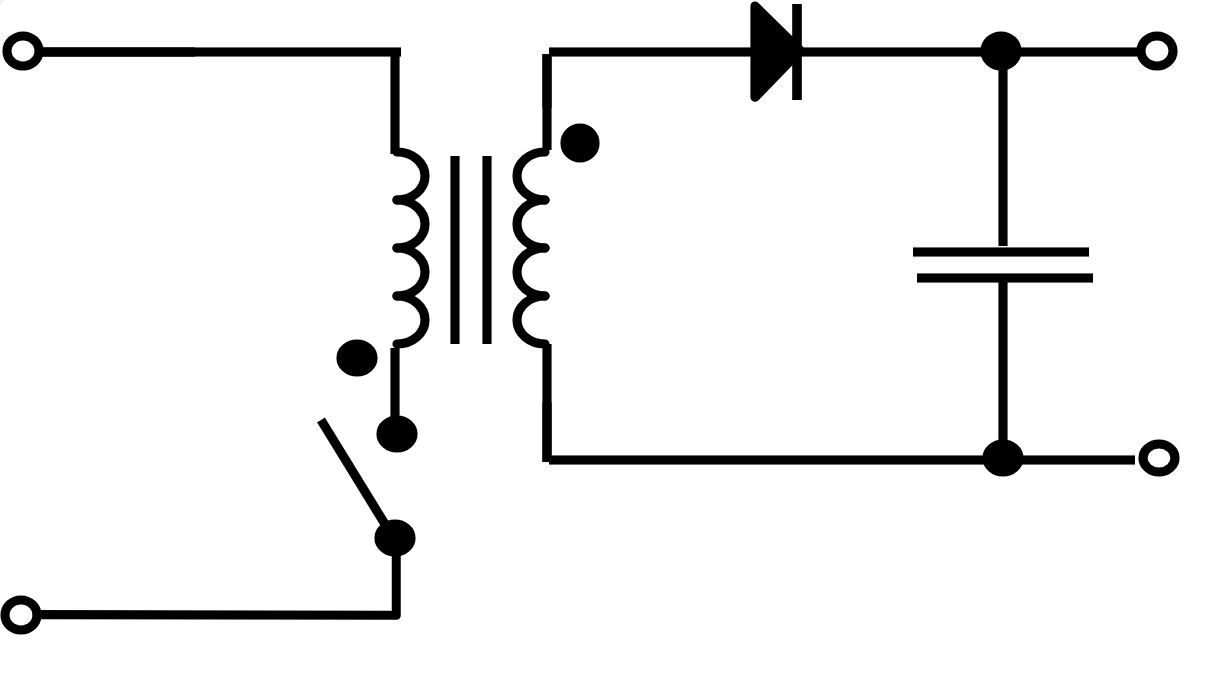

Schema voor enkel AC werking#

In heel wat implementaties is een DC pad naar de belasting niet gewenst. Hierbij denken we bijvoorbeeld aan een luidspreker. Een DC stroom bij een luidspreker geeft een vaste offset van de conus die de lucht aanstuurt. Dit geeft heel wat verliezen en geeft ook een asymmetrische weergave van het geluid. Dit geeft belangrijke vervormingen en ook ook ongewenste hoger tonen.

In Bfig1AC zien we de condensator \(C_{out}\) aan de uitgang. Deze zorgt ervoor dat er geen DC stroom naar de uitgang loopt. Deze condensator wordt na het opstarten opgeladen tot de gemiddelde spanning van de emitters van beide powertransistors. Normaal is deze spanning de helft van \(V_{DD}\) maar indien er een andere gemiddelde spanning op deze knoop zit zal deze condensator deze offset opvangen.

Om de AC uitgangsignalen zo goed mogelijk door te laten, is het aangewezen \(C_{out}\) zo groot mogelijk te nemen. Van de andere kant moet er natuurlijk ook me rekening gehouden worden dat hoe groter \(C_{out}\) is, hoe langere het duurt eer de evenwichtswaarde op de condensator bekomen wordt. Bovendien wordt \(C_{out}\) duurder als hij groter wordt gekozen.

Om de AC ingangsignalen zo goed mogelijk door te laten, is het aangewezen \(C_{in}\) zo groot mogelijk te nemen. Ook hier gelden de aspecten van opstarttijd en kostprijs.

Een ander substantieel voordeel van het schema voor AC sturing is dat er maar 1 voeding nodig is. Dit is in vele gevallen een belangrijke besparing op de kost van het circuit.

Figuur 35 Basisschema van de klasse B versterker voor AC werking.#

Aangezien in de meeste gevallen de nodige voedingsspanning voor de AC aansturing (\(V_{DD2}\)) het dubbele is in vergelijking met de aansturing nodig bij het gebruik van \(+V_{DD}\) en \(-V_{DD}\), zullen we in het verder verloop van dit hoofdstuk in eerste instantie de formules afleiden voor \(V_{DD}\). Je kan de in de meeste van deze formules \(V_{DD}\) vervangen door \(\frac{V_{DD}}{2}\) om deze te gebruiken voor AC aansturing.

Figuur 36 Basisschema van de klasse B versterker voor AC werking.#

Gebruik van de voorinstelspanning#

Aangezien de dode zone zoals aangegeven in Figuur 32 en Figuur 33 duidelijk problematisch is voor de werking van het schema in de buurt van de nuldoorgang, is het aanbrengen van een voorinstelspanning tussen beide basissen van de vermogentransistors eerste dat moet gebeuren om een nuttig klasse B versterkerschema te bekomen. We kunnen op 3 manieren een voorinstelspanning bekomen:

Aan de hand van een weerstand tussen de NPN en de PNP transistor

Aan de hand van een aantal diodes tussen de pull-up transistors en de pull-down transistors

Aan de hand van een circuit met een NPN transistor tussen de pull-up transistors en de pull-down transistors

Naast het circuit dat voor de voorinstelspanning zorgt tussen beide bassissen moeten we natuurlijk ook ervoor zorgen dat de nodige stroom kan vloeien vanuit \(V_{DD}\) naar de basis van de NPN transistor en vanuit de basis van de PNP transistor naar ofwel -\(V_{DD}\) of de grond. Hiervoor kiezen we in eerste instantie de twee weerstanden \(R_1\) en \(R_2\). In een later stadium zullen we hiervoor ook betere alternatieven voorstellen.

Hiermee rekening houdende worden deze 3 mogelijkheden hieronder uitgewerkt.

Weerstand als voorinstelspanning#

De keuze van een weerstand als voorinstelspanning is in eerste instantie de meest eenvoudige om te implementeren (zie Figuur 37). Deze implementatie heeft echter verschillende nadelen.

We willen met de voorinstelspanning de spanning van de basis-emitter diode nauwkeurig volgen. Deze diodespanning gaat dalen bij toenemende temperatuur, waardoor de stroom verder gaat stijgen als de spanning dezelfde blijft. De stijging van de stroom gaat dan de interne temperatuur nog verder laten toenemen waardoor dit onstabiele effect zichzelf versterkt.

Als er variaties op de voedingsspanning zijn, gaan deze variaties een invloed hebben op de voorinstelspanning.

Figuur 37 Basisschema van de klasse B versterker met weerstand als voorinstelspanning.#

Diodes als voorinstelspanning#

Figuur 38 Basisschema van de klasse B versterker voor DC werking met diode voorinstelspanning.#

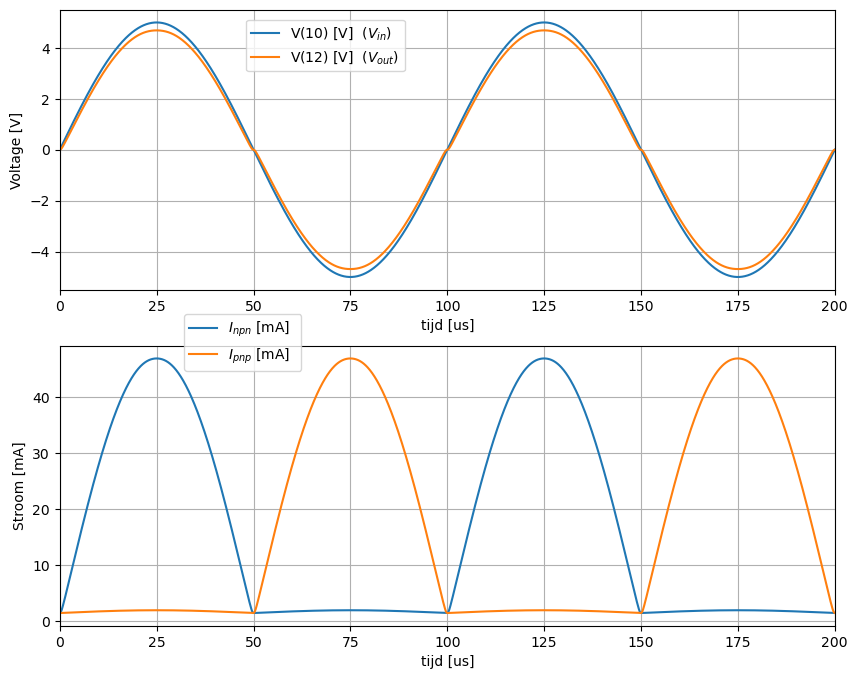

Hieronder tonen we de spice listing van de klasse B versterker waarbij we een voorinstelspanning voorzien tussen de basissen van de npn en de pnp transistor. Deze voorinstelspanning is hier uitgevoerd door diodes. in Figuur 40 merken we hierbij op dat dit tot gevolg heeft dat er toch een stroom blijft lopen door de transistor die niet in geleiding is. Dit noemen we de klasse AB werking van deze klasseB versterker.

Klasse B versterker

*

* SUPPLY VOLTAGES

VPOS 8 0 DC +15V

VNEG 9 0 DC -15V

*

VS2 10 0 DC 0 SIN(0V 5VPEAK 10KHZ)

*

D1 13 10 DNOM

RB1 13 8 10K

Q11 8 13 12 QNPN

*

D2 10 14 DNOM

RB2 14 9 10K

Q12 9 14 12 QPNP

*

RL2 12 0 100

*

* DEVICE MODELS

.model QNPN NPN(BF=50)

.model QPNP PNP(BF=50)

.model DNOM D()

Klasse B versterker

*

* SUPPLY VOLTAGES

VPOS 8 0 DC +15V

VNEG 9 0 DC -15V

*

VS2 10 0 DC 0 SIN(0V 5VPEAK 10KHZ)

*

D1 13 10 DNOM

RB1 13 8 10K

Q11 8 13 12 QNPN

*

D2 10 14 DNOM

RB2 14 9 10K

Q12 9 14 12 QPNP

*

RL2 12 0 100

*

* DEVICE MODELS

.model QNPN NPN(BF=50)

.model QPNP PNP(BF=50)

.model DNOM D()

Figuur 39 Klasse B circuit met voorinstelspanning#

Figuur 40 De klasse B versterker: stromen en spanningen als functie van de tijd.#

In de grafiek (Figuur 41) wordt dit nog duidelijker.

Figuur 41 De klasse B versterker: de stroom door een npn transistor als functie van de spanning.#

Transistor als voorinstelspanning#

Figuur 42 Basisschema van de klasse B versterker voor DC werking met een transistor als voorinstelspanning.#

Driver stage#

Om de vermogentransistors van de klasse B versterker goed aan te sturen, zijn er, naast de voorinstelling tussen beide transistors, ook nog de elementen nodig die het pull-up gedeelte stroom vanuit de voeding \(V_{DD}\) levert en die stroom vanuit het pull-down gedeelte afvoert naar -\(V_{DD}\) of naar de grond. In de bovenstaande schema’s wordt dat gedaan door respectievelijk \(R_1\) en \(R_2\). We kunnen de aansturing nog een stuk efficienter maken door de pull-down afvoer te implementeren met een transistor, zoals je kan zien in Figuur 43. We merken op dat de transistor in de driver stage werkt als een Klasse A versterker met het geheel van de klasse B versterker als belasting. Dat wil zeggen dat deze transistor ook de juiste instelling moet krijgen. Voor de verdere invulling van de transistor in de driver stage verwijzen we naar het hoofdstuk van de Klasse A versterker. Een belangrijk voordeel is hier ook dat deze driver stage niet alleen de stroom versterkt maar ook de spanning. Dit wil zeggen dat we niet noodzakelijk een full swing ingangsignaal nodig hebben om een full swing output signaal te kunnen bekomen.

Figuur 43 Basisschema van de klasse B versterker met driver stage.#

In Figuur 43 zien we dat de werking van de weerstand \(R_1\) eigenlijk het omgekeerde is als we zouden willen. Als de uitgang \(V_{out}\) 0V is, staat er veel spanning over \(R_1\) en levert \(R_1\) dus veel stroom, terwijl er weinig stroom nodig is. Omgekeerd, wanneer de uitgang \(V_{out}\) dicht bij \(V_{DD}\) is staat er weinig spanning over \(R_1\) en levert \(R_1\) dus heel weinig stroom. Het is eigenlijk beter \(R_1\) te vervangen door een constante stroombron. We zien een implementatie hiervan in Figuur 44.

Figuur 44 Basisschema van de klasse B versterker met stroombron.#

Verhoging van het afgeleverde vermogen#

De power transistors in een klasse B versterker werken in principe als spanningsvolgers (met een offset) maar zijn in staat veel meer stroom te leveren aan de belasting (RL) dan de driver trap. In principe kan elke power transistor de stroom met een factor βF vergroten. In een aantal gevallen is deze stroomversterking nog niet voldoende. In deze sectie bespreken we de mogelijkheden om meer stroomversterking te bekomen.

Het Darlington Transistor paar#

We kunnen meer driver stroom bekomen door 2 power transistors van hetzelfde type achter elkaar te schakelen, zoals in Figuur 45. De totale stroomversterking die we dan bekomen is dan het product van beide stroomversterkingen [2].

Figuur 45 Darlington paar.#

Darlington

*

* PUSH-PULL TRANSISTOR OUTPUT STAGE

Q1 3 1 2 QNPN

Q2 3 2 0 QNPN

*

* DEVICE MODELS

.model QNPN NPN(BF=50)

Figuur 46 Transfer characteristiek Darlington paar#

Het schema in Figuur 45 heeft echter 3 problemen:

thermal runaway

lage stroomversterking \(\beta_F\) bij heel lage stromen aan de basis

De voorinstelspanning moet verdubbelen.

We kunnen de configuratie van het Darlington paar verbeteren door emitter degeneratie toe te voegen aan de eerste transistor (zie Figuur 47).

Op het eerste zicht lijkt het dat het schema in Figuur 47 ook een dubbele voorinstelspanning gaat nodig hebben, maar dat is niet het geval. De voorinstelspanning in enkel belangrijk bij kleine ingangssignalen, dus in de buurt van de nuldoorgang. Bij deze signalen speelt de tweede transistor geen enkele rol, als we de emitterdegeneratie doorgevoerd hebben.

Figuur 47 Darlington paar met emitter degeneratie.#

Darlington met emitter degeneratie

*

* PUSH-PULL TRANSISTOR OUTPUT STAGE

Q1 3 1 2 QNPN

Q2 3 2 0 QNPN

RED 2 0 100

*

* DEVICE MODELS

.model QNPN NPN(BF=50)

Figuur 48 Transfer characteristiek Darlington paar met emitter degeneratie#

Het is natuurlijk belangrijk dat we zowel voor de NPN als voor de PNP de stroom vergroten aan de hand van een Darlingtonpaar. Het schema dat er bekomen wordt, kan uitgewerkt worden voor elk van de bovenstaande Klasse B versterkerschemas. Wanneer we dit doen voor het schema in Bfig1AC bekomen we het schema in Figuur 49

Figuur 49 De klasse B versterker met 2 opeenvolgende drive transistors.#

Wanneer we een Darlington paar toevoegen in het schema van Figuur 44 krijgen we het schema in Figuur 50

Figuur 50 Klasse B versterker met Darlington paar.#

Opdracht 1 (Toevoeging van Darlington transistorparen)

Vervang de vermogentransistors in elk van de schema’s van de voorinstelspanning door Darlington transistorparen

Het complementaire Darlington Transistor paar#

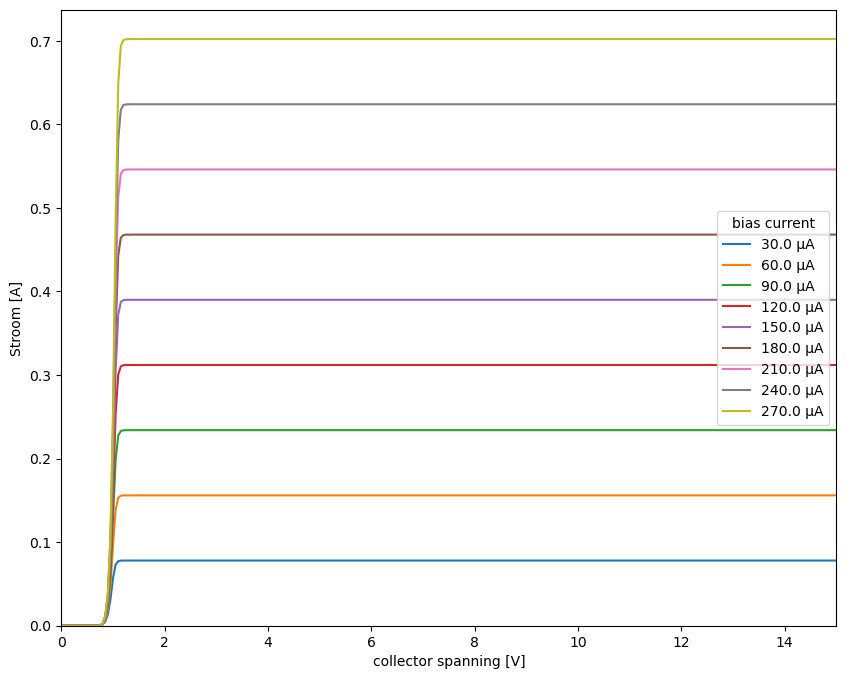

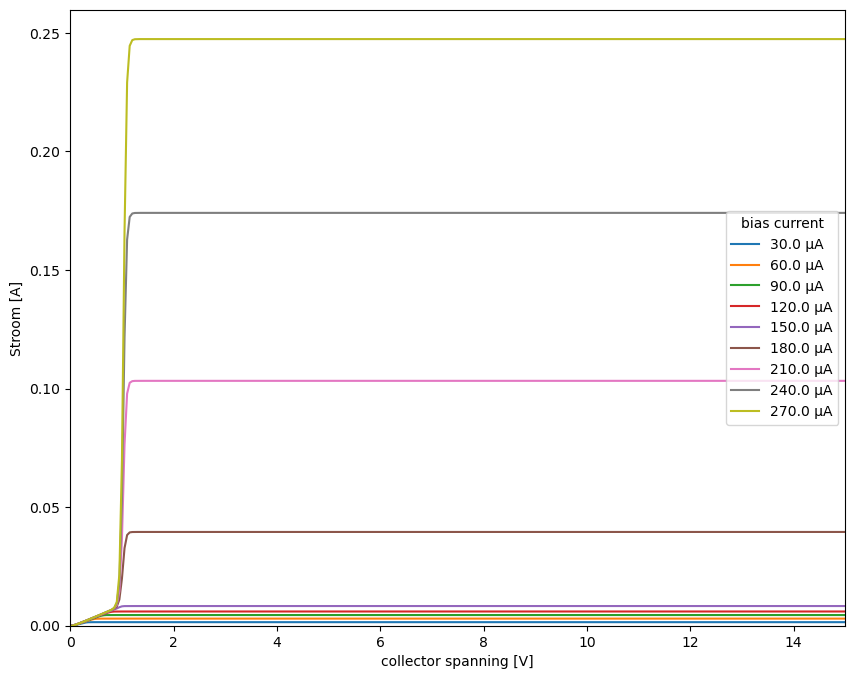

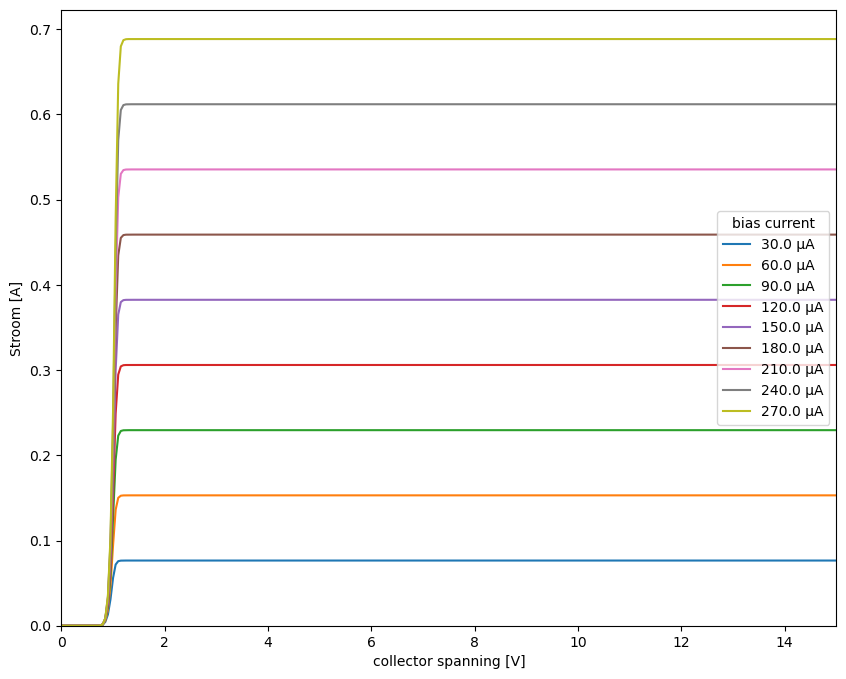

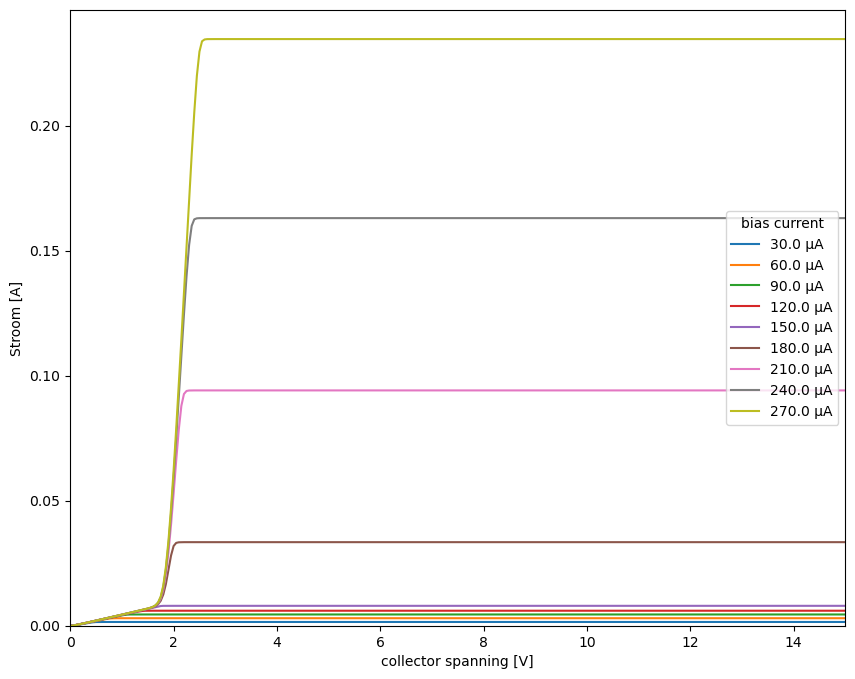

Figuur 51 toont het schema van complementaire transistor paar en spice_Darlington_comp toont de spice code om de werking van dit Darlington paar te simuleren aan de hand van 2 ideale transistors met een \(\beta_F\) van 50. Het resultaat (in Figuur 52) toont dan ook een stroomversterking van 2500 van zodra de emmitter-collectorspanning groter is dan ongeveer 0.7 V.

Figuur 51 Complementair Darlington paar#

Complementaire Darlington met emitter degeneratie

*

* PUSH-PULL TRANSISTOR OUTPUT STAGE

Q1 2 1 0 QNPN

Q2 0 2 3 QPNP

*

* DEVICE MODELS

.model QNPN NPN(BF=50)

.model QPNP PNP(BF=50)

Figuur 52 Transfer characteristiek complementair Darlington paar#

Ook voor dit schema is het relevant om emitter-degeneratie in te voeren. Figuur 53 toont dit schema met emitter-degeneratie. De spice code is te vinden in listingComp_Darlington_ed. We merken in Figuur 54 dat we een \(\beta_F\) van ongeveer 50 bekomen zolang de basisstroom beneden de 150 \(\mu A\) is, en daarboven wordt de \(\beta_F\) 2500.

Figuur 53 Complementair Darlington paar met emitter degeneratie#

Complementaire Darlington met emitter degeneratie

*

* PUSH-PULL TRANSISTOR OUTPUT STAGE

Q1 2 1 4 QNPN

Q2 0 2 3 QPNP

RED 4 0 100

R2 2 3 100

*

* DEVICE MODELS

.model QNPN NPN(BF=50)

.model QPNP PNP(BF=50)

Figuur 54 Transfer characteristiek complementairDarlington paar met emitter degeneratie#

PNP vermogentransistors zijn

minder goed,

minder robust,

minder betrouwbaar,

of duurder

dan de vergelijkbare NPN component.

We vervangen de grootste PNP transistors door NPN transistors.

T’2 verhuist daardoor van plaats en we moeten de diode terug invoeren.

We zijn een belangrijk deel van de symmetrie terug kwijt.

Efficiëntie van de Klasse B versterker#

De theoretische berekening van de efficiëntie als functie van de uitsturing benaderen we in eerste instantie door enkel de stroom van het pull-up netwerk en het pull down netwerk te bekijken.

met de uitsturing (x) gedefinieerd als \(\frac{V_{ac}}{V_{DD}}\).

Dissipatie per transistor#

De dissipatie is maximaal voor een uitsturing van 63%.

Deze dissipatie is kleiner dan de helft van het maximale AC vermogen.

Per transistor is dit maar 1/4 van het maximale AC vermogen.

Bij een klasse A is de maximale dissipatie het dubbele van het maximale AC vermogen.

Voor een gelijk vermogen zullen de transistors van een klasse A versterker ongeveer 10 maal groter (en duurder) zijn.

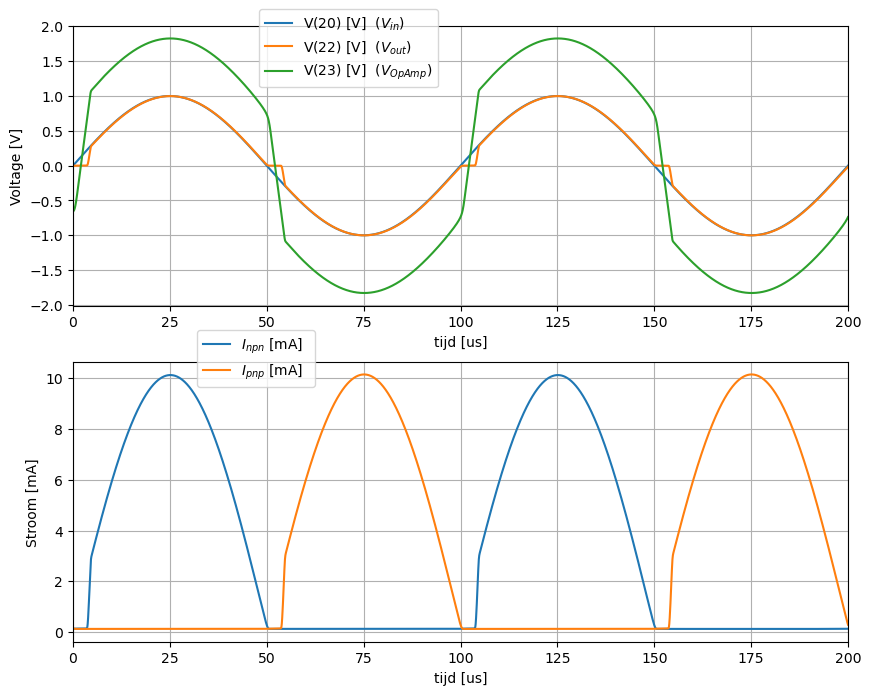

Invoering van terugkoppeling#

We kunnen ook proberen de dode zone weg te werken aan de hand van feedback, zoals in het onderstaande schema aan de hand van een opamp. Op het eerste zicht lijkt dat te lukken, als we de simulatie in Figuur 55 bekijken. De \(V_{in}\) en \(V_{out}\) liggen zo goed als volledig op elkaar dat we het verschil niet merken. Enkel als we heel erg inzoomen, zoals in Figuur 56 lijkt er een klein verschil te zijn langs de nuldoorgang. Laat je hierbij echter niet vangen. Deze simulatie is gedaan met een ideale OpAmp, waarvan de stijgsnelheid niet realistisch is. Wanneer we diezelfde simulatie hernemen met een realistische OpAmp, zie onder, blijft dit bijna ideale gedrag niet behouden.

Klasse B versterker met OPAMP terugkoppeling

VPOS 8 0 DC +15V

VNEG 9 0 DC -15V

VS3 20 0 DC 0 SIN(0V 5VPEAK 10KHZ)

Q21 8 23 22 QNPN

Q22 9 23 22 QPNP

RL3 22 0 100

XOpAmp 20 22 8 9 23 8 opamp

* DEVICE MODELS

.model QNPN NPN(BF=50)

.model QPNP PNP(BF=50)

.model DNOM D()

Figuur 55 De klasse B versterker teruggekoppeld met een ideale OpAmp: stromen en spanningen als functie van de tijd.#

Figuur 56 De klasse B versterker teruggekoppeld met een ideale OpAmp: stromen en spanningen als functie van de tijd in de nabijheid van de nuldoorgang.#

Figuur 57 De klasse B versterker: de stroom door een npn transistor als functie van de spanning.#

Klasse B versterker met OPAMP terugkoppeling

VPOS 8 0 DC +2.5V

VNEG 9 0 DC -2.5V

VS3 20 0 DC 0 SIN(0V 1VPEAK 10KHZ)

Q21 8 23 22 QNPN

Q22 9 23 22 QPNP

RL3 22 0 100

XOpAmp 20 22 8 9 23 8 opamp

* DEVICE MODELS

.model QNPN NPN(BF=50)

.model QPNP PNP(BF=50)

.model DNOM D()

Figuur 58 De klasse B versterker met lagere voedingsspanning teruggekoppeld met een ideale OpAmp: stromen en spanningen als functie van de tijd.#

Echter, wanneer we een realistisch model van een opamp invoeren, zoals de LMV981-N van Texas Instruments, zien we een heel ander gedrag in de dode zone.

Nodige Voedingsspanning#

Beveiliging van de Klasse B vermogentransistors#

Waar en hoe is beveiliging nodig?#

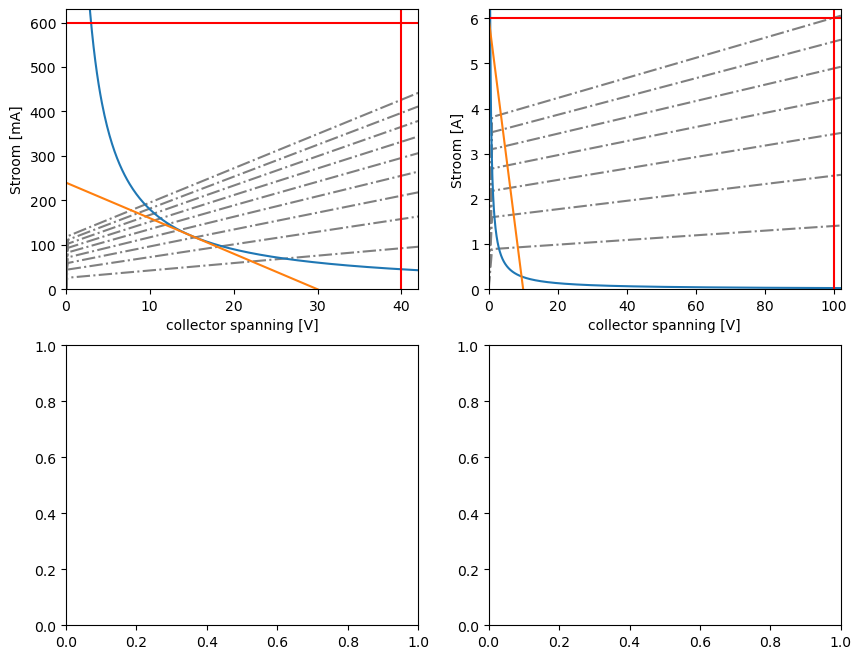

Als eerste voorbeeld gebruiken we hier de 2N2222A NPN transistor. Dit is een typische NPN transistor die reeds ontwikkeld werd in 1962 met een βF van ongeveer 100. De datasheet geeft de nodige details over de maximale stroom (600 mA), maximale spanning (40V) en maximaal vermogen (1.8W). Zonder extra koeling toe te voegen zien we dat hier de maximale vermogenbegrenzing de bepalende factor gaat zijn. Wanneer we een begrenzing kiezen die lineair verloopt tussen een kortsluitstroom van 240 mA en open-klemmen spanning van 30V kunnen verhinderen dat deze transistor te warm wordt (oranje lijn in Figuur 60). Het is duidelijk dat voor vele vermogenversterkers deze transistor te beperkt is.

De datasheets en spice modellen van heel wat meer recente transistors kunnen we online terugvinden. De MJD41C is geschikt voor maximale stromen tot 6A en spanningen tot 100V.

Figuur 60 Beveiliging van bipolaire transistors op maximale stroom, maximale spanning en maximaal vermogen.#

Beveiliging tegen overstroom#

Figuur 61 toont een eerste schema dat beveiliging tegen overstroom toevoegt. Het basisprincipe bij elke stroombeveliging is dat er gekeken wordt naar de stroom aan de uitgang van respectievelijk het pull-up en het pull-down netwerk (de groene blokken in Figuur 61). Wanneer de stroom hier de hierboven aangegeven maximale stroom overschrijdt, grijpt het blok dat gekleurd is in Cyaan in. Dit gebeurt door de stroom aan de ingang van het groene blok rechtstreeks naar de uitgang te verbinden.

Figuur 61 Beveiliging van bipolaire transistors op maximale stroom.#

Figuur 62 Klasse B versterker met overstroombescherming.#

We merken op dat de overstroombeveiliging moet optreden bij de maximale stroom. In dit geval zal, in het geval van een Darlington paar, ook de tweede transistor actief zijn. Dit heeft dan ook tot gevolg dat we het schema van Figuur 62 moeten uitbreiden met een extra diode in het geval van een Darlington paar. Dit tonen we in Figuur 63.

Figuur 63 Klasse B versterker met overstroombescherming.#

Een belangrijk nadeel van de schema’s hierboven is dat ze slechts ingrijpen bij overstroom als de spanning over de weerstand RI ongeveer 0.7V bedraagt. Dit is normaal geen probleem als er gewerkt wordt met een hoge voedingsspanning VDD, bv 80V. Indien er echter met een lage voedingsspanning gewerkt wordt, geeft het spanningsverlies over RI een belangrijk deel van het vermogenverlies. Een alternatieve oplossing om dat vermogenverlies te voorkomen is het plaatsen van een veel kleinere meetweerstand RI tussen de belasting en de grond en de gemeten spanning te versterken in de terugkoppeling of de aanstuur IC.

De oplossing in Figuur 64 is wel een minder robuuste oplossing, aangezien deze afhangt van de terugkoppeling en/of de IC, en dat het daardoor minder zeker is dat de beveiliging in alle omstandigheden zal ingrijpen.

Figuur 64 Klasse B versterker met overstroombescherming in de load#

Beveiliging tegen overspanning#

Het basisconcept van een beveiliging tegen overspanning is dat de spanning over de transistor gemeten wordt aan de hand van een weerstand.

Figuur 65 Beveiliging van bipolaire transistors op maximale spanning.#

Figuur 66 Klasse B versterker met overspanningsbescherming.#

Beveiliging tegen te hoog vermogen.#

De beveiliging tegen te hoog vermogen voeren we in door een lineaire combinatie van de beveiliging tegen te hoge stroom en de beveiliging tegen te hoge spanning. De spanning aan de basis van \(T_B\) (\(V_b(T_B)\))is de som van de spanning over \(R_I\) (\(V_{over}(R_I)\)) en de spanning over \(R_{v1}\). Deze laatste herschrijven we dan weer als een spanningsdeling van de spanning over de vermogentransistors.

Als we stellen dat de beveiligingstransistor ingrijpt wanneer de basis-emitterspanning 0.7V wordt, is de vergelijking xx de vergelijking van een rechte in de outputkarakteristiek van de vermogentransistor. In de outputkarakteristiek plotten we \(I_{door}\) als functie van \(V_{over}\), zoals getoond in Figuur 60. Door de parameters \(R_{v1}\), \(R_{v2}\) en \(R_{I}\) juist te kiezen bepalen we de gewenste beveiliging.

Figuur 67 Beveiliging van bipolaire transistors op maximale stroom, maximale spanning en maximaal vermogen.#

In Figuur 68 passen we dit concept toe vertrekkende van het schema van Figuur 50.

Figuur 68 Klasse B versterker met bescherming tegen overspanning,overstroom en te groot vermogen.#

Filtering aan de ingang#

In de meeste gevallen zijn er ook ongewenste signalen aan de ingang en het is niet efficient om deze ook mee te versterken.

Daarom is het efficient om deze signalen weg te filteren aan de ingang.

In Bfig1AC wordt dit reeds gedaan voor de DC component in het signaal. Deze is niet nuttig indien we enkel het AC signaal aan de uitgang bekomen. We kunnen echter een heel stuk beter doen.

Hoogdoorlaatfilter aan de ingang#

Figuur 69 toont hoe we een hoogdoorlaatfilter aan de ingang van een klasse B versterker kunnen realiseren.

Figuur 69 Klasse B versterker met hoogdoorlaatfilter aan de ingang.#

Merk op dat in Figuur 69 de weerstand Rf ook dienst doet als bias weerstand van de driver transistor, aangezien −VDD < 0. De nodige bias stroom van deze transistor bepaalt dus de keuze van Rf. Dit wil zeggen dat alleen Cf kan gebruikt worden om de hoogdoorlaatfilter te ontwerpen.

Laagdoorlaatfilter aan de ingang#

Figuur 70 toont hoe we een laagdoorlaatfilter aan de ingang van een klasse B versterker kunnen realiseren.

Figuur 70 Klasse B versterker met laagdoorlaatfilter aan de ingang.#

We merken op dat in Figuur 70 de weerstand Rf de ingang (Vin) belast. We moeten bij het ontwerpen van de driver van Vin ermee rekening houden dat deze de nodige stroom hiervoor moet kunnen leveren.

Banddoorlaatfilter aan de ingang#

De hoogdoorlaatfilter in Figuur 69 en de laagdoorlaatfilter in Figuur 70 kunnen gecombineerd worden in een banddoorlaatfilter zoals getoond wordt in Figuur 71. Dit is de meest eenvoudige oplossing om een banddoorlaatfilter te bekomen overeenstemmende met de gewenste karakteristieken van het signaal. Er zijn heel wat mogelijkheden om nog veel betere ingangsfilters te ontwerpen. Dit is echter niet het doel van deze cursus. Hiervoor verwijzen we naar de cursus toegepaste analoge Elektronica [3]

Figuur 71 Klasse B versterker met Banddoorlaatfilter aan de ingang.#

Figuur 72 toont de bandpass filter op zich, in de veronderstelling dat de stroom door \(R_{f2}\) veel groter is dan de ingangsstroom aan de basis van de driver transistor. In dat geval mogen we deze basisstroom verwaarlozen en kunnen we stellen dat de uitgangsspanning van het filter bekomen wordt door de spanningsdeling van de 2 impedanties \(Z_1\) en \(Z_2\) als:

met

en

Hieruit volgt:

We kunnen dit verder uitwerken tot:

We zien dat we 1 nulpunt en 2 polen hebben voor \(j \omega\). Deze 2 polen vinden we door de vierkantsvergelijking van de noemer op te lossen naar \(j \omega\). De doorlaatband is bepaald door de band tussen de pool bij de laagste frequentie en de pool bij de hoogste frequentie.

Figuur 72 Banddoorlaatfilter voor aan de ingang.#

Zelftest via Flashcards#

Klik op de vraag als je je antwoord wil nakijken. Klik op next om de volgende vraag te bekomen.